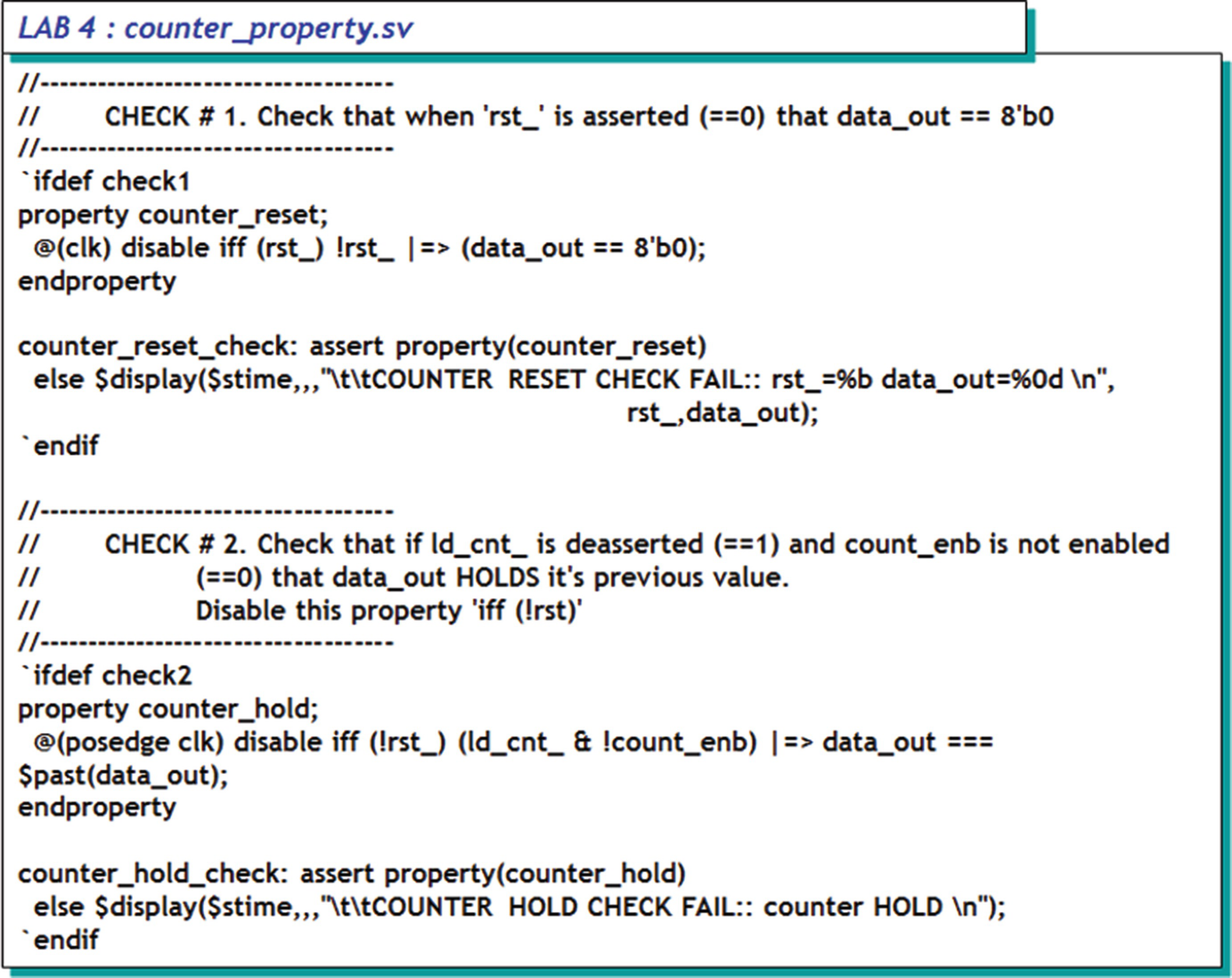

`ifdef, `ifndef, `elsif, `else and `endif conditionally compiles Verilog code, depending on whether or not a specified macro is defined Any code that is not compiled must still be valid Verilog code `include includes the contents of another Verilog source fileSystem Verilog Macro A Powerful Feature for Design Verification Projects By Ronak Bhatt, Verification Engineer, eInfochips For any design verification (DV) project, following best coding practices make life easier for the teammates On the other hand, bad coding style leads to a lot of issues when the code is reused, or when it is handedThen specify this file first in the list of Verilog files to import I'd be interested to know if it works (I don't have time to try it myself) to solve problems and get the most

Verilog Archives Verification Guide

Verilog ifdef check value

Verilog ifdef check value-Aug 25, 10 · Verilog lacks an `if, and as such the preprocessor can't directly perform math Math would allow more metaprogramming features, but it's probably worth leaving out to avoid suffering bugs similar to those in C, where "#ifdef"s are often mistyped forFor this to work, you need to read the defines with the below at the bottom of your file Verilogmode will use the last definition of SUB_CELL to determine which one to pickup the pinlist from

1996 Verilog Hdl A Guide To Digital Design And Synthesis B By Chanraksmey Ly Issuu

Always @ (posedge clk) begin `ifdef (param == 0) // < counterA Verilog HDL keyword preceded by an escape character is not interpreted as a keyword All keywords are defined in lowercase Therefore, you must be type them in lowercase in source files 3 Data Types Data types represent the data storage and transmission elements of digital hardware Value Set The value set consists of four basic valuesJun 17, 17 · The painfull verilog preprocessor pitfall Just a little note about how includes and `defines work in verilog which is VERY different from how they behave in most programming languages This may not really hurt in a small project, but can become a real PITA in a big project with a dozen of thirdparty blocks

Reg 30 counter = 0;Enhanced Literal Value Assignments QIn Verilog, the vector size must be hard coded in order to fill all bits with 1 reg 1270 data_bus;Oct 04, 15 · Verilog takes the two assignment statements as happening at the same time in parallel Verilog simulator to establish initial values For example Syntax In Assignment Statement L Value Verilog Ifdef Legal lefthand side forms in assignment statements details onOverriding Module Parameter Values Example VerilogXL schedules a subsequent assignment to Syntax In

Mar 22, · Verilog Quiz MCQs Interview Questions 1 The default value for reg data type is ______ 2 The possible value (s) of the == operator are 3 To suspend a simulation, you can use this system task command 4 ______ operator usually comes before the operand 6May 08, 17 · As Keith Thompson explained undefined tokens (macros) like cocos2d and x evaluate to 0 so you need to define values for the macros you're using If I understand this correctly, cocos2dx is one of several possible APIs The preprocessor can test whether a symbol is defined or not (using #ifdef and the defined operator), and it can evaluateMay , 18 · Verilog `ifdef Appears Questionable Jump to solution Foo_TBenv is a Verilog test bench, acting to call module ModuleFoo with a clock input and an 8bit data value which increments in each clock cycle Foov defines ModuleFoo, which acts to accept the clock and 8bit data in, register the data, and output the registered data

Encore Sim Editor Software User Guide

Ppt Verilog For Computer Design Powerpoint Presentation Free Download Id

Where the parameter assignment can be by name or by the order of the valuesValue — Any combination of the 4 basic values can be digits for radix octal, decimal or `ifdef cond // If cond is defined, compile the following `else `endif 8 Operators Operator Verilog has special syntax restriction on using both reduction and bitwise operatorsThe `define compiler directive is used to perform global macro substitution and remain active for all files read/compiled after the macro definition It will available until another macro definition changes the value or until the macro is undefined using the `undef compiler directive `define WIDTH 8 to avoid redefincation `ifdef can be used, `ifdef WIDTH // do nothing (better to use `ifndef) `else `define WIDTH 8 `endif `ifndef WIDTH `define WIDTH

System Verilog Assertions Lab Answers Springerlink

Pdf Real Portable Models For System Verilog A Ams

Mar 11, 21 · `ifdef SUB_IS_A_FOOBAR `define SUB_CELL foobar `else `define SUB_CELL foobiz `endif `SUB_CELL subcell (/*AUTOINST*/);The #ifdef, #ifndef , #elseif, #elif, #else, and

0 件のコメント:

コメントを投稿